”fpga开发 时序约束 vivado 建立时间保持时间“ 的搜索结果

文档详细讲述时序约束的定义,并使用vivado结合例子讲解,适合初学者学习FPGA开发

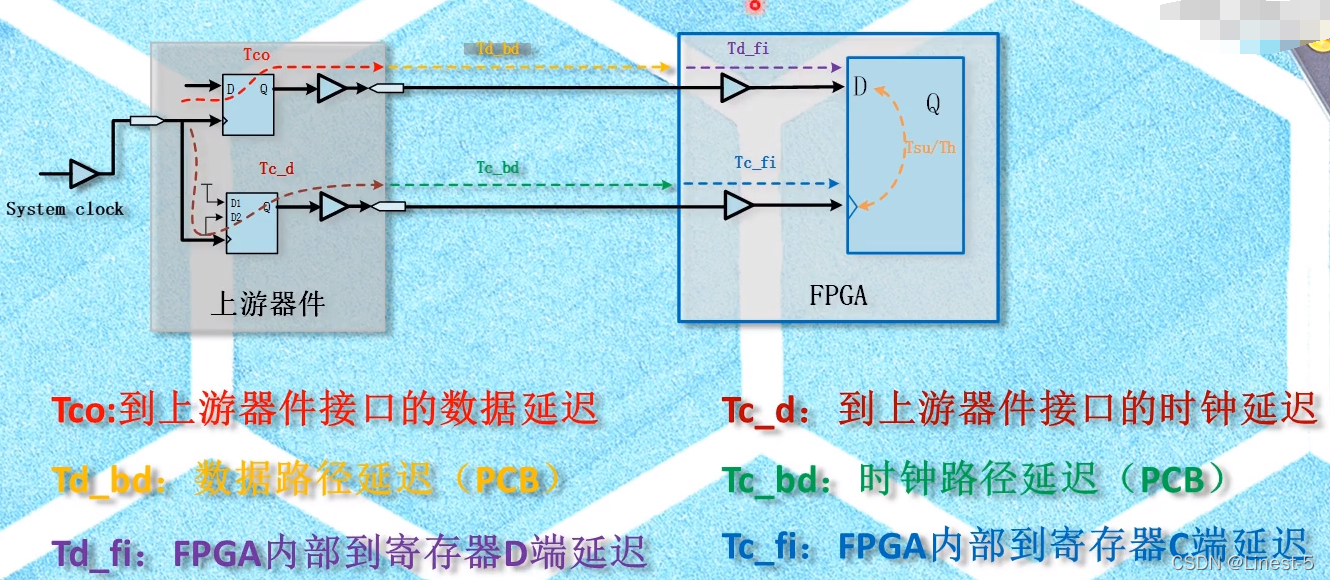

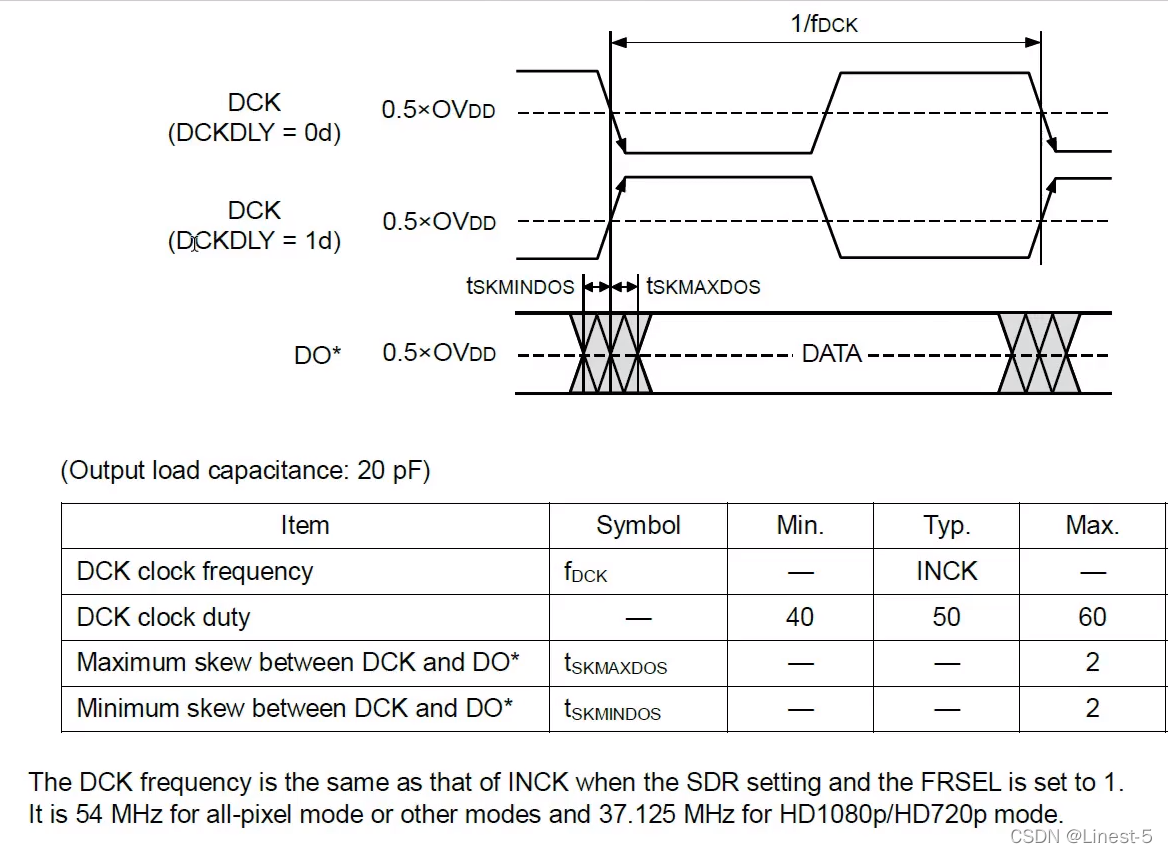

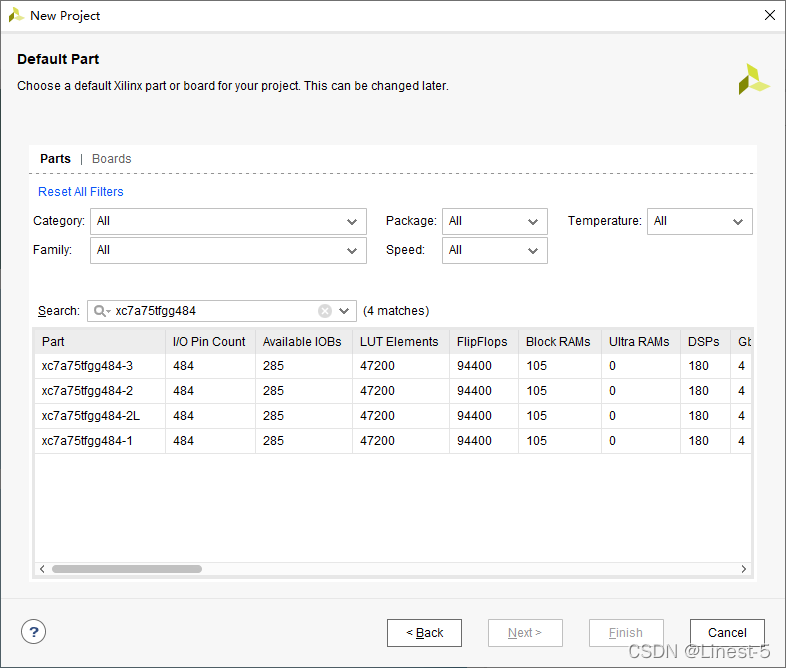

基于Xilinx Vivado输入延迟约束分析工程实操,通过此实验工程可以更加深刻的分析输入延迟约束。

介绍使用Vivado进行时序约束相关操作

如何在Vivado中添加时序约束,Vivado添加约束的方法有3种:xdc文件、时序约束向导(Constraints Wizard)、时序约束编辑器(Edit Timing Constraints )

对于时钟约束本人用到的不多,也处于一边学习一别补充当中。

vivado时序约束

标签: fpga开发

上面我们讲的都是xdc文件的方式进行时序约束,Vivado中还提供了两种图形界面的方式,帮我们进行时序约束:时序约束编辑器(Edit Timing Constraints )和时序约束向导(Constraints Wizard)。两者都可以在综合...

本文将详细介绍如何读懂Vivado时序报告,包括报告的基本结构和如何分析报告。

vivado 如何添加时序约束

标签: 时序

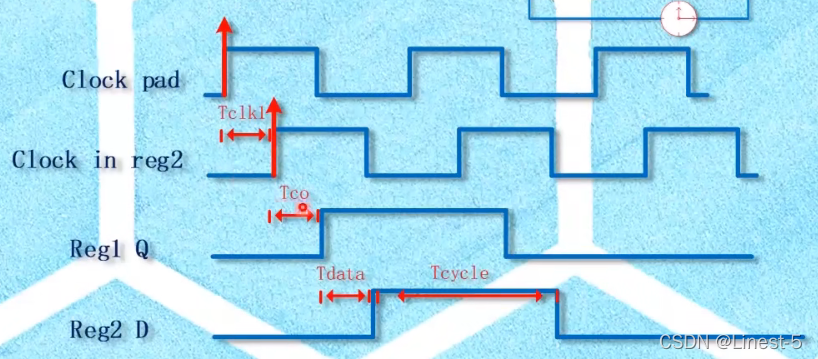

本文介绍了FPGA时序约束的基础理论知识,希望通过阅读本文,大家能够更好地理解时序约束原理,并在实际工作中运用这些原理提高设计效率和准确性。

时钟之间的两个方向上的时间被忽略。这是一般不常使用,举例如下:create_clock -name clk_virt -period 10,定义一个名称为clk_virt,周期为10ns的虚拟时钟。系统抖动是由电源噪声、电路板噪声或系统的任何额外抖动...

Vivado时序约束基础

标签: fpga开发

首先时钟约束必须最早创建,对于7系列FPGA来说,端口进来的时钟和GT的输出RXCLK/TXCLK都必须用create_clock自主创建为主时钟,如果是差分输入的时钟,可以仅仅在差分对的P侧用get_ports获取端口,并使用create_clock...

前两篇文章介绍了什么是亚稳态?以及静态时序分析,但那些终究还是理论,那么在实际工程中,如何分析时序路径呢?如何将理论转到实际呢?

首先来看什么是时序约束,泛泛来说,就是我们告诉软件(Vivado、ISE等)从哪个pin输入信号,输入信号要延迟多长时间,时钟周期是多少,让软件PAR(Place and Route)后的电路能够满足我们的要求。因此如果我们不加...

推荐文章

- ImportError: cannot import name Template解决方案_importerror: cannot import name 'prompttemplate' f-程序员宅基地

- Laravel随笔 Windows下Redis安装/php安装redis扩展_windows laravel 8使用 phpredis 扩展来连接 redis-程序员宅基地

- 同声传译免费软件app哪个好?让国际交流变得轻松又有趣-程序员宅基地

- 一文详解opencv摄像头数字识别_摄像头数字识别在其他场景下识别不了-程序员宅基地

- TCP三次握手四次挥手详解_tcp三次挥手四次挥手-程序员宅基地

- 域账户信息导出脚本_Facebook OAuth漏洞导致的Facebook账户劫持-程序员宅基地

- docker中容器和镜像的关系_docker镜像和容器的关系-程序员宅基地

- idea运行java报错:找不到或无法加载主类_idea找不到或无法加载java主类-程序员宅基地

- java scriptengine,使用Java ScriptEngine(Groovy),如何使它更具性能?-程序员宅基地

- docker项目运行环境搭建(JDK8、mysql8、tomcat9、redis5、nginx1.14)_docker jdk8-程序员宅基地